Жаропонижающие средства для детей назначаются педиатром. Но бывают ситуации неотложной помощи при лихорадке, когда ребенку нужно дать лекарство немедленно. Тогда родители берут на себя ответственность и применяют жаропонижающие препараты. Что разрешено давать детям грудного возраста? Чем можно сбить температуру у детей постарше? Какие лекарства самые безопасные?

Нажав на кнопку "Скачать архив", вы скачаете нужный вам файл совершенно бесплатно.

Перед скачиванием данного файла вспомните о тех хороших рефератах, контрольных, курсовых, дипломных работах, статьях и других документах, которые лежат невостребованными в вашем компьютере. Это ваш труд, он должен участвовать в развитии общества и приносить пользу людям. Найдите эти работы и отправьте в базу знаний.

Мы и все студенты, аспиранты, молодые ученые, использующие базу знаний в своей учебе и работе, будем вам очень благодарны.

Чтобы скачать архив с документом, в поле, расположенное ниже, впишите пятизначное число и нажмите кнопку "Скачать архив"

Подобные документы

Анализ вариантов проектных решений и выбор на его основе оптимального решения. Синтез функциональной схемы микропроцессорной системы на основе анализа исходных данных. Процесс разработки аппаратного и программного обеспечения микропроцессорной системы.

курсовая работа , добавлен 20.05.2014

Теоретические основы разработки микропроцессорной системы на основе микроконтроллера и устройства для чтения электронных книг, анализ их технико-экономических показателей и сравнение с аналогами. Основные нормы по охране труда при работе с компьютером.

дипломная работа , добавлен 13.07.2010

Целесообразность применения МП-устройства. Архитектура микропроцессорной системы. Структурная организация БИС ВТ с изолированными шинами. Содержание и возможная направленность микроконтроллера. Обобщенная структура простого встраиваемого микроконтроллера.

реферат , добавлен 28.04.2011

Структура микропроцессорной системы, алгоритм ее управления и передачи сигналов. Карта распределения адресов. Разработка электрической принципиальной схемы и выбор элементной базы. Расчет потребляемого тока, блока питания, программного обеспечения.

курсовая работа , добавлен 22.01.2014

Распределение функций между аппаратной и программной частями микропроцессорной системы. Выбор микроконтроллера, разработка и описание структурной, функциональной и принципиальной схемы. Выбор среды программирования, схема алгоритма и листинг программы.

курсовая работа , добавлен 17.08.2013

Назначение и устройство микропроцессорной системы контроля. Описание функциональной схемы микропроцессорной системы контроля. Расчет статической характеристики канала измерения. Разработка алгоритма функционирования микропроцессорной системы контроля.

курсовая работа , добавлен 30.08.2010

Общее понятие о микроконтроллерах, их использование и назначение. Разработка проекта микропроцессорной системы сбора данных с использованием стендов SDK 1.1 и SDX 0.9. Создание программного обеспечения и его загрузка в лабораторный стенд SDK-1.1.

курсовая работа , добавлен 31.01.2014

Введение

Специальность «Компьютерные системы и сети» – одна из важнейших и наиболее универсальных в современной системе образования. В сферу ее интересов входят самые разнообразные объекты и устройства управления – от элементарных регуляторов до сложнейших систем управления производственными процессами и экспериментальными исследованиями.

Ввиду многоцелевого характера разработки и производства средств вычислительной техники важнейшее значение приобретает проблема дальнейшего повышения их эффективности, определяемой системой структурно-функциональных характеристик.

За последние годы в микроэлектронике бурное развитие получило направление, связанное с выпуском микроконтроллеров, которые предназначены для «интеллектуализации» оборудования различного назначения. Микроконтроллеры представляют собой приборы, конструктивно выполненные в виде БИС и включающие в себя все основные части «голой» микроЭВМ: микропроцессор, память программ и память данных, а также программируемые интерфейсные схемы для связи с внешней средой. Использование микроконтроллеров в системах управления обеспечивает достижения исключительно высоких показателей эффективности при столь низкой стоимости (во многих применениях система может состоять только из одной БИС микроконтроллера), что микроконтроллерам, видимо, нет разумной альтернативной элементной базы для построения управляющих и / или регулирующих систем.

К настоящему времени более двух третей мирового рынка микропроцессорных средств составляют именно микроконтроллеры.

Структурная организация, набор команд и аппаратурно-программные средства ввода-вывода информации микроконтроллеров лучше всего приспособлены для решения задач управления и регулирования в приборах устройствах и системах автоматики, а не для решения задач обработки данных.

1. Анализ технического задания

В данной курсовой работе необходимо спроектировать микропроцессорную систему на основе микроконтроллера К1816ВЕ31. Требуется описать и разработать структурную и функциональную схемы проектируемого устройства (системы), обосновать выбор конкретных элементов, разработать принципиальную схему проектируемого устройства (системы), разработать программу инициализации основных компонентов, а также программу функционирования на языке ассемблера микроконтроллера.

2. Разработка структурной схемы проектируемого устройства

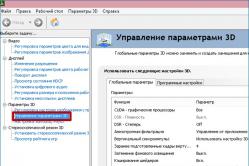

Основу структурной схемы микроконтроллера (рисунок 1) образует внутренняя двунаправленная 8-битная шина, которая связывает между собой все основные узлы и устройства: резидентную память, АЛУ, блок регистров специальных функций, устройство управления и порты ввода / вывода.

Арифметико-логическое устройство. 8-битное АЛУ может выполнять арифметические операции сложения, вычитания, умножения и деления; логические операции И, ИЛИ, исключающее ИЛИ, а также операции циклического сдвига, сброса, инвертирования и т.п. В АЛУ имеются программно недоступные регистры Т1 и Т2, предназначенные для временного хранения операндов, схема десятичной коррекции и схема формирования признаков.

Простейшая операция сложения используется в АЛУ для инкрементирования содержимого регистров, продвижения регистра-указателя данных и автоматического вычисления следующего адреса РПП. Простейшая операция вычитания используется в АЛУ для декрементирования регистров и сравнения переменных.

Простейшие операции автоматически образуют «тандемы» для выполнения в АЛУ таких операций, как, например, инкрементирование 16-битных регистровых пар. В АЛУ реализуется механизм каскадного выполнения простейших операций для реализации сложных команд. Так, например, при выполнении одной из команд условной передачи управления по результату сложения в АЛУ трижды инкрементируется СК, дважды производится чтение из РПД, выполняется арифметическое сравнение двух переменных, формируется 16-битный адрес перехода и принимается решение о том, делать или не делать переход по программе. Все перечисленные операции выполняются в АЛУ всего лишь за 2 мкс.

Важной особенностью АЛУ является его способность оперировать не только байтами, но и битами. Отдельные программно-доступные биты могут быть установлены, сброшены, инвертированы, переданы, проверены и использованы в логических операциях. Эта способность АЛУ оперировать битами столь важна, что во многих описаниях микропроцессора говорится о наличии в нем «булевского процессора». Для управления объектами часто применяются алгоритмы, содержащие операции над входными и выходными булевскими переменными (истина / ложь), реализация которых средствами обычных микропроцессоров сопряжена с определенными трудностями.

Рисунок -1. Структурная схема КР1816ВЕ31

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется 51 различная операция пересылки или преобразования этих данных. Используется 11 режимов адресации (7 для данных и 4 для адресов), путем комбинирования «операция / режим адресации» базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции

Резидентная память . Память программ и память данных, размещенные на кристалле КР1816ВЕ31, физически и логически разделены, имеют различные механизмы адресации, работают под управлением различных сигналов и выполняют различные функции.

Память программ (ПЗУ или СППЗУ) имеет емкость 4Кбайта и предназначена для хранения команд, констант, управляющих слов инициализации, таблиц перекодировки входных и выходных переменных и т.п. РПП имеет 16-битную шину адреса, через которую обеспечивается доступ из счетчика команд или из регистра-указателя данных. Последний выполняет функции базового регистра при косвенных переходах по программе или используется в командах, оперирующих с таблицами.

Память данных (ОЗУ) предназначена для хранения переменных в процессе выполнения прикладной программы, адресуется одним байтом и имеет емкость 128 байт. Кроме того, к адресному пространству РПД примыкают адреса регистра специальных функций (РСФ), которые перечислены в таблице 3.

Память программ, также как и память данных, может быть расширена до 64Кбайт путем подключения внешних БИС.

Аккумулятор и ССП . Аккумулятор является источником операнда и местом фиксации результата при выполнении арифметических, логических операций и ряда операций передачи данных. Кроме того, только с использованием аккумулятора могут быть выполнены операции сдвига, проверка на нуль, формирование флага паритета и т.п.

Таблица 3.1

| Символ | Наименование | Адрес |

| * АСС | Аккумулятор | 0Е0Н |

| * В | Регистр-расширитель аккумулятора | 0F0Н |

| * PSW | Слово состояния программы | 0D0H |

| SP | Регистр-указатель стека | 81Н |

| DPTR | Регистр-указатель данных (DPH) |

|

| * P0 | Порт 0 | 80Н |

| * Р1 | Порт 1 | 90Н |

| * Р2 | Порт 2 | 0А0Н |

| * Р3 | Порт 3 | 0В0Н |

| * IP | Регистр приоритетов | 0В8Н |

| * IE | Регистр маски прерываний | 0А8Н |

| TMOD | Регистр режима таймера / счетчика | 89Н |

| * TCON | Регистр управления / статуса таймера | 88Н |

| TH0 | Таймер 0 (старший байт) | 8СН |

| TL0 | Таймер 0 (младший байт) | 8АН |

| TH1 | Таймер 1 (старший байт) | 8DН |

| TL1 | Таймер 1 (младший байт) | 8BН |

| Символ | Наименование | Адрес |

| * SCON | Регистр управления приемопередатчиком | 98Н |

| SBUF | Буфер приемопередатчика | 99Н |

| PCON | Регистр управления мощностью | 87Н |

Примечание. Регистры, имена которых отмечены знаком (*), допускают адресацию отдельных бит.

Таблица. 3.2

| Символ | Позиция | Имя и назначение |

| С | PSW.7 | Флаг переноса. Устанавливается и сбрасывается аппаратурными средствами или программой при выполнении арифметических и логических операциях |

| АС | PSW.6 | Флаг вспомогательного переноса. Устанавливается и сбрасывается только аппаратурными средствами при выполнении команд сложения и вычитания и сигнализирует о переносе или займе в бите 3. |

| F0 | PSW.5 | Флаг 0. Может быть установлен, сброшен или проверен программой как флаг, специфицируемый пользователем. |

| Выбор банка регистров. Устанавливается и сбрасывается программой для выбора рабочего банка регистров (см. примечание) | ||

| OV | PSW.2 | Флаг переполнения. Устанавливается и сбрасывается аппаратно при выполнении арифметических операций. |

| – | PSW.1 | Не используется. |

| Р | PSW.0 | Флаг паритета. Устанавливается и сбрасывается аппаратно в каждом цикле команды и фиксирует нечетное / четное число единичных бит в аккумуляторе, т.е. выполняет контроль по четности. |

Примечание. Выбор рабочего банка регистров

| RS1 | RS0 | Банк | Границы адресов |

| 0 | 0 | 0 | 00Н-07Н |

| 0 | 1 | 1 | 08Н-0FH |

| 1 | 0 | 2 | 10H-17H |

| 1 | 1 | 3 | 18H-1FH |

При выполнении многих команд в АЛУ формируется ряд признаков операции (флагов), которые фиксируются в регистре ССП. В таблице 4 приводится перечень флагов ССП, даются их символические имена и описываются условия их формирования.

Наиболее «активным» флагом ССП является флаг переноса, который принимает участие и модифицируется в процессе выполнения множества операций, включая сложение, вычитание и сдвиги. Кроме того, флаг переноса (С) выполняет функции «булевого аккумулятора» в командах, манипулирующих с битами. Флаг переполнения (OV) фиксирует арифметическое переполнение при операциях над целыми числами со знаком и делают возможным использование арифметики в дополнительных кодах. АЛУ не управляет флагами селекции банка регистров (RS0, RS1), и их значение полностью определяется прикладной программой и используется для выбора одного из четырех регистровых банков.

Структурная схема микроконтроллерной системы приведена в графической части курсового проекта приложение А

3. Разработка функциональной схемы микроконтроллерной системы

Разработка подсистемы памяти

В микроконтроллерных системах, построенных на основе КР1816ВЕ31, возможно использование двух типов внешней памяти: постоянной памяти программ (ВПП) и оперативной памяти данных (ВПД). Доступ к ВПП осуществляется при помощи управляющего сигнала RD, который выполняет функцию строб-сигнала, чтения. Доступ к ВПД обеспечивается управляющими сигналами RD и WR, которые формируются в линиях Р3.7 и Р3.6 при выполнении портом 3 альтернативных функций.

При обращении к ВПП всегда используется 16-битный адрес. Доступ к ВПД возможен с использованием 16-битного адреса (MOVXA,@DPTR) или 8-битного адреса (MOVXA,@RI).

В любых случаях использования 16-битного адреса старший байт адреса фиксируется (и сохраняется неизменным в течение одного цикла записи или чтения) в регистре-защелке порта 2.

Если очередной цикл внешней памяти (MOVXA,@DPTR) следует не сразу же за предыдущим циклом внешней памяти, то неизменяемое содержимое регистра-защелки порта 2 восстанавливается в следующем цикле. Если используется 8-битный адрес (MOVXA,@RI), то содержимое регистра-защелки порта 2 остается неизменным на его внешних выводах в течение всего цикла внешней памяти.

Через порт 0 в режиме временного мультиплексирования осуществляется выдача младшего байта адреса и передача байта данных. Сигнал САВП должен быть использован для записи байта адреса во внешний регистр. Затем в цикле записи выводимый байт данных появляется на внешних выводах порта 0 только перед появлением сигнала . В цикле чтения вводимый байт данных принимается в порт 0 по фронту стробирующего сигнала .

При любом обращении к внешней памяти устройство управления КР1816ВЕ31 загружает в регистр защелку порта 0 код 0FFH, стирая тем самым информацию, которая могла в нем храниться.

Доступ к ВПП возможен при выполнении двух условий: либо на вход отключения резидентной памяти программ () подается активный сигнал, либо содержимое счетчика команд превышает значение 0FFFH. Наличие сигнала необходимо для обеспечения доступа к младшим 4К адресам адресного пространства ВПП при использовании КР1816ВЕ31.

Основная функция сигнала САВП – обеспечить временное согласование передачи из порта 0 на внешний регистр младшего байта адреса в цикле чтения из ВПП. Сигнал САВП приобретает значение 1 дважды в каждом машинном цикле. Это происходит даже тогда, когда в цикле выборки нет обращения к ВПП. Доступ к ВПД возможен только в том случае, если сигнал САВП отсутствует. Первый сигнал САВП во втором машинном цикле команды MOVX блокируется. Следовательно, в любой МК-системе, не использующей ВПД, сигнал САВП генерируется с постоянной частотой, равной 1/16 частоты резонатора, и может быть использован для синхронизации внешних устройств или для реализации различных временны функций.

При обращении к РПП сигнал не генерируется, а при обращении к ВПП он выполняет функцию строб-сигнала чтения. Полный цикл чтения ВПД, включая установку и снятия сигнала , занимает 12 периодов резонатора.

Особый режим работы КР1816ВЕ31 . Содержимое памяти программ КР1816ВЕ31заполняется единожды на этапе разработки МК-системы и не может быть модифицировано в завершенном изделии. По этой причине микроконтроллеры не являются машинами классической «фон-неймановской» архитектуры. Оперативная память данных не может быть использована для хранения кодов программы. Эта особенность архитектуры МК объясняется тем, что в большинстве применений МК требуется наличие одной неизменяемой прикладной программы, хранимой в ПЗУ, наличие ОЗУ небольшой емкости для временного хранения переменных и эффективных, а следовательно, разных методов адресации памяти программ и памяти данных.

Микроконтроллер КР1816ВЕ31 не имеет внутренней памяти программ и поэтому пользуется только внешней памятью, которую можно модифицировать путем перепрожига внешней микросхемы ПЗУ.

Тип микропроцессора К1816ВЕ31. Объем внешнего ОЗУ – 4Кбайт. В данном микропроцессоре (в соответствии со структурой команд) внешняя адресация памяти данных позволяет адресовать 64Кбай внешней памяти. Для разработки подсистемы памяти выбираем микросхему в соответствии с перечнем элементов, приведенных в приложении Г.

Разработка подсистемы временных характеристик

Регистры специальных функций . Регистры с символическими именами IP, IE, TMOD, TCON, SCON и PCON используются для фиксации и программного изменения управляющих бит и бит состояния схемы прерывания, таймера / счетчика, приемопередатчика последовательного порта и для управления мощностью электропитания КР1816ВЕ31

Последовательный порт К1816ВЕ31 может работать в четырех различных режимах.

Режим 0. В этом режиме информация и передается и принимается через внешний вывод входа приемника (RXD). Принимаются или передаются восемь бит данных. Через внешний вывод выхода передатчика (ТXD), выдаются импульсы сдвига, которые сопровождают каждый бит. Частота передачи бита информации равна 1/12 частоты резонатора.

Режим 1 . В этом режиме передаются через ТXD или из RXD принимаются десять бит информации: старт-бит (0), восемь бит данных и стоп-бит. Скорость приема / передачи – величина переменная и задается таймером.

Режим 2 . В этом режиме передаются через ТXD или из RXD принимаются одиннадцать бит информации: старт-бит, восемь бит данных, программируемый девятый бит и стоп-бит. При передаче девятый бит данных может принимать значение 0 или 1, или, например, для повышения достоверности передачи путем контроля по четности в него может быть помещено значение признака паритета из слова состояния программы (PSW.0). Частота приема / передачи выбирается программой и может быть равна либо 1/32, либо 1/64 частоты резонатора в зависимости от управляющего бита SMOD.

Режим 3 . Совпадает с режимом 2 во всех деталях, за исключением частоты приема / передачи, которая является величиной переменной и задается таймером.

Управление режимом работы УАПП осуществляется через специальный регистрSCON. Этот регистр содержит не только управляющие биты, определяющие режим работы последовательного порта, но и девятый бит принимаемых или передаваемых (RB8 и TB8) и биты прерывания приемопередатчика (RI и TI).

Прикладная программа путем загрузки в старшие биты спецрегистра SCON 2-битного кода определяет режим работы УАПП. Во всех четырех режимах работы передача из УАПП инициируется любой командой, в которой буферный регистр SBUF указан как получатель байта. Прием в УАПП в режиме 0 осуществляется при условии, что RI=0 и RЕN=1. В режиме 1,2,3 прием начинается с приходом старт-бит, если RЕN=1.

В бите ТВ8 программно устанавливается значение девятого бита данных, который будет передан в режиме 2 или 3. В бите RВ8 фиксируется в режимах 2 и 3 девятый принимаемый бит данных. В режиме 1, если SМ2=0, в бит RВ8 заносится стоп-бит. В режиме 0 бит RВ8 не используется.

Флаг прерывания передатчика TIустанавливается аппаратно в конце периода передачи восьмого бита в режиме 0 и в начале передачи стоп-бита в режиме 1,2 и 3. Соответствующая подпрограмма обслуживания должна сбрасывать бит ТI.

Флаг прерывания приемника RIустанавливается аппаратно в конце периода передачи восьмого бита в режиме 0 и в середине приема стоп-бита в режиме 1,2 и 3. Подпрограмма обслуживания прерывания должна сбрасывать бит RI.

Скорость приема / передачи информации по линии связи определяется в начале работы над курсовым проектом и равна 600 бод.

Программируемый таймер находится внутри микроконтроллера К1816ВЕ31.

Таймер/счетчик . В составе средств КР1816ВЕ31 имеются регистровые пары с символическими именами TH0, TL0 и TH1, TL1, на основе которых функционируют два независимых программно-управляемых 16-битных таймера / счетчика событий.

Два программируемых 16-битных таймера / счетчика (Т/С0 и Т/С1) могут быть использованы в качестве таймеров или счетчиков внешних событий. При работе в качестве таймера содержимое Т/С инкрементируется в каждом машинном цикле, т.е. через каждые 12 периодов резонатора. При работе в качестве счетчика содержимое Т/С инкрементируется под воздействием перехода из 1 в 0 внешнего входного сигнала, подаваемого на соответствующий (Т0, Т1) вывод К1816ВЕ31. Опрос значения внешнего входного сигнала выполняется в момент времени S5P2 каждого машинного цикла. Содержимое счетчика будет увеличено на 1 в том случае, если в предыдущем цикле был считан входной сигнал высокого уровня (1), а в следующем – сигнал низкого уровня (0). Новое значение счетчика будет сформировано в момент S3P1 в цикле в следующем за тем, в котором был обнаружен переход сигнала из 1 в 0. Так как на распознавание перехода требуется два машинных цикла, то максимальная частота подсчета входных сигналов равна 1/24 частоты резонатора. На длительность периода входных сигналов ограничений сверху нет. Для гарантированного прочтения входного считаемого сигнала он должен удерживать значение 1 как минимум в течении одного машинного цикла К1816ВЕ31.

Для управления режимами работы Т/С и для организации взаимодействия таймеров с системой прерывания используются два регистра специальных функций (РРТС и РУСТ). Как следует из описания управляющих бит РРТС, для обоих Т/С режимы работы 0, 1 и 2 одинаковы. Режимы 3 для Т/С0 и Т/С1 различны. Рассмотрим кратко работу Т/С во всех четырех режимах.

Режим 0 . Перевод любого Т/С в режим 0 делает его похожим на таймер МК48 (8-битный счетчик), на вход которого подключен 5-битный предделитель частоты на 32. В этом режиме таймерный регистр имеет разрядность 13 бит. При переходе из состояния» все единицы» в состояние «все нули» устанавливается флаг прерывания от таймера TF1. Входной синхросигнал таймера 1 разрешен (поступает на вход Т/С), когда управляющий бит TR1 установлен в 1 и либо управляющий бит GATE (блокировка) равен 0, либо выход запроса прерывания поступает уровень 1.

В таблице 8 приведены регистры режима работы таймера / счетчика, а в таблице 9 регистры управления / статуса таймера.

Установка бита GATE в 1 позволяет использовать таймер для измерения длительности импульсного сигнала, подаваемого на вход запроса прерывания.

Таблица 4.2.1

| Символ | Позиция | Имя и назначение |

| GATE | TMOD.7 для T/С1 и TMOD.3 для T/C0 | Управление блокировкой. Если бит установлен, то таймер / счетчик «х» разрешен до тех пор, пока на входе «INTx» высокий уровень и бит управления «TRx» установлен. Если бит сброшен, то Т/С разрешается, как только бит управления «TRx» устанавливается. |

| TMOD.6 для T/С1 и TMOD.2 для T/C0 | Бит выбора режима таймера / счетчика событий. Если бит сброшен, то работает таймер от внутреннего источника сигналов синхронизации. Если бит установлен, то работает счетчик от внешних сигналов на входе «Тх». | |

| М1 | TMOD.5 для T/С1 и TMOD.1 для T/C0 | Режим работы (см. примечание). |

| М0 | TMOD.4 для T/С1 и TMOD.0 для T/C0 | |

| М1 | М0 | Режим работы |

| 0 | 0 | Таймер МК48. «TLx» работает как 5-битный предделитель. |

| 0 | 1 | 16-битный таймер / счетчик. «THx» и «TLx» включены последовательно. |

| 1 | 0 | 8-битный автоперезагружаемый таймер / счетчик. «THx» хранит значение, которое должно быть перезагружено в «TLx» каждый раз по переполнению. |

| 1 | 1 | Таймер/счетчик1 останавливается. Таймер/счетчик0: TL0 работает как 8-битный таймер / счетчик, и его режим определяется управляющими битами таймера0.TH0 работает только как 8-битный таймер, и его режим определяется управляющими битами таймера1. |

Режим 1 . Работа любого Т/С в режиме 1 такая же, как и в режиме 0, за исключением того, что таймерный регистр имеет разрядность 16 бит.

Режим 2 . В режиме 2 работа организована таким образом, что переполнение (переход из состояния» все единицы» в состояние «все нули») 8-битного счетчика TL1 приводит не только к установке флага TF1, но и автоматически перезагружает в TL1 содержимое старшего байта (TH1) таймерного регистра, которое предварительно было задано программным путем.

Режим 3 . В режиме 3 Т/С0 и Т/С1 работают по разному. Т/С 1 сохраняет неизменным свое текущее содержимое. Иными словами, эффект такой же как и при сбросе управляющего бита TR1 в ноль.

В режиме 3 TL0 и TH0 функционируют как два независимых 8-битных счетчика. Работу TL0 определяет управляющие биты Т/С 0 (, GATE, TR0), входной сигнал и флаг переполнения TF0. Работу ТН0, который может выполнять только функции таймера (подсчет машинных циклов МК), определяет управляющий бит TR1. При этом ТН0 использует флаг переполнения TF1.

Разработка подсистемы связи с центральной ЭВМ

Проектируемое устройство должно выдавать содержимое памяти в центральную ЭВМ, а также принимать информацию от центральной ЭВМ.

Т.к. обмен информацией осуществляется на большие расстояния, то передачу необходимо вести в последовательном формате. Преобразование данных из параллельного формата в последовательный и обратно выполняет УАПП. УАПП – универсальный асинхронный приемопередатчик, предназначенный для реализации двунаправленного асинхронного обмена данными, представленными в параллельном формате, и управляющими словами с микропроцессором, а также двунаправленного асинхронного обмена данными, представленными в последовательном формате с другими модулями системы, например видеотерминалами, накопителями на магнитной ленте и т.д. Таким образом, УАПП преобразует параллельный код, полученный из системы по шине данных, в последовательный, и поразрядно выдаёт его в канал связи, а также выполняет обратное преобразование.

В состав УАПП, называемого часто последовательным портом, входят принимающий и передающий сдвигающий регистры, а также специальный буферный регистр (SBUF) приемопередатчика. Запись байта в буфер приводит к автоматической переписи байта в сдвигающий регистр передатчика и инициирует начало передачи байта. Наличие буферного регистра приемника позволяет совмещать операцию чтения ранее принятого байта с приемом очередного байта. Если к моменту окончания приема байта предыдущий байт не был считан из SBUF, то он будет потерян.

Управление режимом работы УАПП осуществляется через специальный регистр с символическим именем SCON. Этот регистр содержит не только управляющие биты, определяющие режим работы последовательного порта, но и девятый бит принимаемых или передаваемых данных (RB8 и TB8) и биты прерывания приемопередатчика (R1 и T1).

Таблица 4.5.1

| Символ | Позиция | Имя и назначение |

| TF1 | TCON.7 | Флаг переполнения таймера1. Устанавливается аппаратурно при переполнении таймера / счетчика. Сбрасывается при обслуживании прерывания аппаратурно |

| TR1 | TCON.6 | Бит управления таймера 1. Устанавливается/сбрасывается программой для пуска / останова. |

| TF0 | TCON.5 | Флаг переполнения таймера1. Устанавливается аппаратурно. Сбрасывается при обслуживании прерывания |

| TR0 | TCON.4 | Бит управления таймера 0. Устанавливается/сбрасывается программой для пуска / останова. таймера / счетчика. |

| IE1 | TCON.3 | |

| IT1 | TCON.2 | Бит управления типом прерывания 1. Устанавливается / сбрасывается программой для спецификации запроса (срез / низкий уровень). |

| IE0 | TCON.1 | Флаг фронта прерывания 1. Устанавливается аппаратурно, когда детектируется срез внешнего сигнала . Сбрасывается при обслуживании прерывания |

| IT0 | TCON.0 | Бит управления типом прерывания 0. Устанавливается / сбрасывается программой для спецификации запроса (срез / низкий уровень). |

Режим 3 используется в тех случаях применение К1816ВЕ31, когда требуется наличие дополнительного 8-битного таймера или счетчика событий. Можно считать, что в режиме 3 К1816ВЕ31 имеет в своем составе 3 таймера / счетчика. В том случае, если Т/С0 используется в режиме 3, Т/С1 может быть или включен или выключен, или переведен в свой собственный режим 3, или может быть использован последовательным портом в качестве генератора частоты передачи, или, на конец, может быть использован в любом применении, не требующим прерывания.

После определения скорости приема / передачи информации необходимо обеспечить тактовую частоту приема RxC, передачи ТхС. Выдача этих синхросигналов осуществляется с использованием каналов программируемого таймера. Исходная частота, поступающая на программируемый таймер, равна частоте разрабатываемой микропроцессорной системы. Для определения уставки, записываемой в соответствующий канал программируемого таймера, необходимо определить коэффициент пересчета исходной частоты системы в частоту приема / передачи по линии связи, а также выбрать соответствующий режим работы задействованных каналов таймера.

5. Разработка принципиальной схемы проектируемого устройства

Выбор элементной базы

В контроллере, разрабатываемом в данном курсовом проекте, в качестве центральной части используется однокристальная микроЭВМ КМ1816ВЕ31, выполненная на основе высокоуровневой n -МОП технологии и взаимодействующая со средой в стандарте ТТЛ-схем с тремя состояниями выхода. Это позволяет при разработке схемы использовать ИС из микропроцессорного комплекта серии 580 быстродействующие ТТЛ серии. Как указывалось выше, в состав микроконтроллера входит программируемый таймер, асинхронный последовательный интерфейс (УАПП) и ПЗУ емкостью 1 Кб.

Для построения проектируемого устройства была выбрана следующая элементная база:

Программируемый контроллер клавиатуры и индикации КР580ВВ79;

Статическое ОЗУ емкостью 16Кб АТ28С128;

Блок семисегментных индикаторов АЛС318;

Буферный регистр К1533ИР22;

ПЗУ К573РУ8;

Выбор указанных микросхем обусловлен их совместимостью по уровням, низким энергопотреблением, достаточно высоким быстродействием и помехозащищенностью.

6. Разработка программного обеспечения

Для выполнения поставленных задач микропроцессорной системе необходима программа функционирования, согласно которой микропроцессор будет осуществлять выдачу управляющих сигналов на шину управления, адресов ячеек памяти и устройств на шину адреса и осуществлять обмен данными по шине данных. Т.к. в системе имеются еще и программируемые контроллеры, то для работы с ними необходима так называемая инициализация, являющаяся загрузкой в специальные регистры управляющих слов. Причем инициализация всех контроллеров должна выполнятся до начала выполнения системой задания и один раз после включения питания (исключением является аппаратный системный сброс). Для инициализации системы в качестве управляющих слов для ИМС используются константы, хранящиеся в ПЗУ микроконтроллера.

В системе имеются так же аппаратные прерывания, в результате которых должны выполнятся какие-либо действия, после чего основная программа продолжает свое выполнение. Такие прерывания обслуживают подпрограммы обработки прерываний (в системе их две: подпрограмма обработки прерываний от таймера и подпрограмма обработки прерывания от последовательного интерфейса).

Программу функционирования условно можно разделить на две части: инициализацию и рабочий цикл.

Инициализация представляет собой запись в определенные регистры некоторых констант, определяющих режимы работы процессора и отдельных частей системы.

Рабочий цикл – это набор процедур и операторов, выполняемых в бесконечном цикле, и обеспечивающих выполнение возложенных на систему функций. Граф-схема алгоритма работы и подпрограмм, приведенные на листе 4 графической части.

Подпрограмма инициализации контроллера клавиатуры и индикации

В разработке использован ПККИ типа КР580ВВ79. Его настройка осуществляется загрузкой управляющего слова «установка режима работы контроллера клавиатуры и индикации» в соответствующий регистр блока управления. Режим работы блока интерфейса клавиатуры: последовательный опрос матрицы клавиш с дешифрированием состояния счетчика сканирования и запрещением 2-х или более нажатых клавиш. Режим работы блока индикации: вывод символов на 8-разрядную индикацию с размещением их слева направо.

Рисунок 6.2 – Формат управляющего слова «программный сброс»

Разряды D7 – D5 – адрес управляющего слова «программный сброс»;

Разряды D4 = 0 – коды находящиеся во внутреннем ОЗУ индикации выдаются на выходы OUT; D1 = 1 – обнуление регистра состояния ОЗУ клавиатуры и на выходе IRQ – сигнал низкого уровня; D0 ºD4.

Рисунок 6.4 – Формат управляющего слова «запись в ОЗУ индикации»

Разряды D7-D5 – адрес управляющего слова; D3-D0 – адрес ячейки ОЗУ индикации.

Формат управляющего слова «Чтение многорежимного ОЗУ клавиатуры» аналогичен формату управляющего слова «Чтение из ОЗУ индикации», за исключением содержимого битов D7-D5.

| 0 | 1 | 0 | 1 | х | х | х | х |

Рисунок 6.5 – Формат регистра управляющего слова клавиатуры

Разряды D7-D5 – адрес управляющего слова; D4 – признак автоинкремента; D3-D0 – адрес ячейки ОЗУ клавиатуры.

Подпрограмма инициализации программируемого параллельного интерфейса

Настройка ППИ осуществляется загрузкой управляющего слова в регистр управляющего слова. Настройка производится следующим образом: порт А работает в режиме ввода информации с датчиков через АЦП, а порт В работает в режиме вывода информации на ЦАП. Порт С будет управлять процессами приема и выдачи информации.

В разработанной системе ППИ работает в 0 режиме. Функции этого режима:

1) Два 8-ми разрядных и два 4-х разрядных порта.

2) Все порты могут быть как входными, так и выходными.

3) Выходные порты защелкиваются, входные – нет.

Формат регистра управляющего слова ППИ представлен на рис. 6.6.

Рисунок 6.7 – Формат регистра SCON.

SM1 и SM0 (D7, D6) – определяют режим работы последовательного порта (Режим 2: 9-ти разрядный асинхронный приемопередатчик, фиксированная скорость приемопередачи);

REN (D4) – флаг управления разрешением приема;

TB8 (D3) – установка состояния 9-го бита принимаемых данных;

RB8 (D2) – анализ состояния 9-го бита принимаемых данных;

TI (D1) – бит прерывания по передачи;

RI (D0) – бит готовности.

Подпрограмма опроса клавиатуры

Программируемый контроллер клавиатуры и индикации настраивается на режим чтения многорежимного ОЗУ клавиатуры с автоинкрементом, в счетчик заносим количество ячеек ОЗУ клавиатуры. Происходит последовательный опрос клавиатуры, после чего данные о нажатых функциональных клавишах записываются в ОЗУ клавиатуры.

Подпрограмма выдача данных на индикаторы

При обращении в данную подпрограмму сначала происходит обнуление счетчика, а затем наращивание его до заданного количества индикаторов. Программируемый контроллер клавиатуры и индикации настраивается на режим записи в ОЗУ индикации и происходит последовательный вывод информации на индикаторы. Выход из подпрограммы произойдет после выдачи всех кодов символов на индикаторы.

Опрос датчиков и выдача выходных сигналов

Опрос датчиков и выдача выходных сигналов происходит по следующему алгоритму:

1) в счетчик заносится количество опрашиваемых датчиков;

2) информация считывается с датчиков в порт А, который ранее был проинициализирован на прием данных;

3) принятая информация переписывается через аккумулятор в специально отведенную для информации с датчиков ячейку ОЗУ;

4) уменьшение счётчика количества датчиков на 1;

5) если произошел опрос всех датчиков, то ППИ перестраивается на выдачу информации из порта В;

6) в счетчик заносится количество выходных сигналов;

7) информация из ячейки ОЗУ через аккумулятор заносится в порт В;

8) производится вывод информации.

Подпрограмма обмена информацией с центральной ЭВМ

В этой подпрограмме вначале производится чтение регистра состояния УАПП. После этого выполняется проверка: установлен ли пятый бит регистра в 1. Если установлен, то это означает, что УАПП готов к передаче информации и происходит побитная передача данных в линию связи до тех пор, пока счетчик передаваемых информационных разрядов не будет равен нулю. Как только все информационные разряды передадутся в линию связи, произведутся новые начальные установки (начальный адрес ОЗУ, количество информационных разрядов) и подпрограмма закончит свое выполнение. Если же еще на первом этапе пятый бит регистра не будет установлен в 1, следовательно произойдет выход из подпрограммы, т. к. УАПП в этом случае не готов передавать информацию.

Подпрограмма инициализации таймера

Для управления режимами работы таймера / счетчика и для организации взаимодействия таймеров с системой прерывания используют два специальных регистра: TCON и TMOD.

Рисунок 6.9 – Формат регистра TMOD.

Регистр TMOD задает режимы работы Т/С0 и Т/С1. Устанавливаем для Т/С1 первый режим работы: 16-битный таймер / счетчик. TH1 и TL1 включены последовательно. При переходе из состояния» все единицы» в состояние «все нули» устанавливается флаг прерывания от таймера TF1. Входной синхросигнал таймера 1 разрешен (поступает на вход Т/С), когда управляющий бит TR1 установлен в 1 и либо управляющий бит GATE (блокировка) равен 0, либо выход запроса прерывания поступает уровень 1.), блокировка отключена, таймер работает от внутреннего источника сигналов синхронизации.

Таймер 1 должен быть инициализирован для выдачи частоты синхронизации приема-передачи последовательного порта и для организации прерывания, во время которого подсистема должна будет передать информацию о состоянии аналоговых датчиков и состоянии клавиатуры в центральную ЭВМ.

Производится заполнение таймерных регистров:

В TH1 записывается FEh

В TL1 записывается EBh

Значения TH1 и TL1, обновляются в соответствующих процедурах прерываний.

Заключение

В ходе выполнения курсового проекта были рассмотрены структурная организация, режимы работы, и алгоритмы функционирования микропроцессорного устройства на базе микроконтроллера серии К1816.

В ходе работы над курсовым проектом были разработаны структурная и принципиальная схемы, а также его программное обеспечение, для составления которого использовалась система команд и алгоритм функционирования КМ1816ВЕ31.что позволило понять какие действительно процессы проходят в микроконтроллерной системе и как они выполняются.

Перечень источников

1. Цифровые и аналоговые интегральные микросхемы: Справочник / под ред. С.В. Якубовского. – М: Радио и связь, 1990. – 496 с.

2. Микропроцессоры / К.Г. Самофалов, О.В. Викторов – Киев: Техника, 1989. – 312 с.

3. Справочник по цифровой схемотехнике / И.В. Зубчук, В.П. Сигорский. – К.: Техника, 1990 г. – 448 с.

4. Микросхемы ЦАП и АЦП: функционирование, параметры, применение / Б.Г. Федорков, В.А. Телец – М.: Энергоатомиздат, 1990. 320 с.

5. Сташин В.В., Урусов И.А. Мологонцева И.А. Проектирование цифровых устройств на однокристальных микро-ЭВМ. М. Энергоатомиздат –1990 – 285 с.

логика прерываний запоминает уровень приоритета обслуживаемого прерывания. При выполнении команды RET уровень приоритета сохраняется и следующим может быть обслужено только прерывание с более высоким уровнем приоритета. Команда RETI отличается от команды RET тем, что она сбрасывает уровень приоритета, что позволяет обслуживать запросы на прерывания с низким уровнем приоритета.

К типовым условным операциям относятся команды JZ и JNZ, JC

и JNC. Две последних включены в группу «булевых». В команде CJNE сначала сравниваются, по правилам вычитания целых чисел, два байта

и в соответствии с результатом сравнения устанавливается флаг C. Затем, в случае их несовпадения, выполняется ветвление.

В команде DJNZ в качестве счетчика может использоваться не только один из регистров текущего регистрового банка Rn, n=0...7, но и прямо адресуемая ячейка памяти данных DSEG. При исполнении команды сначала выполняется декремент счетчика и, если содержимое счетчика не равно нулю, ветвление.

3. Проектирование микропроцессорных систем

Технология проектирования МПС на основе микроконтроллеров полностью соответствует концепции неразрывности процесса проектирования и отладки аппаратной и программной составляющих, принятой в микропроцессорной технике. Важной особенностью применения микроконтроллеров является работа в реальном масштабе времени, т.е. гарантированная реакция на внешние события в течение определенного интервала времени. Очевидно, что решение задачи совместной отладки аппаратной и программной составляющих в реальном масштабе времени при произвольной структуре и схемотехнике микропроцессорной системы является весьма сложной, дорогостоящей и долговременной работой.

3.1. Этапы проектирования

Особенностью МПС является то, что сами они встраиваются (интегрируются) в некоторый объект. Это предполагает, что перед разработчиком МПС такого рода стоят задачи полного цикла проектирования, начиная от разработки алгоритма функционирования и заканчивая комплексными испытаниями в составе изделия, а возможно, и сопровождением при производстве. Основные этапы проектирования МПС отображены на рис. 28 .

Технические требования начинают цикл проектирования МПС. Возможность программирования микропроцессорной системы стимулирует заказчика возложить на нее выполнение максимального числа функций. Критерием выбора должна служить экономическая целесообразность любого увеличения объема аппаратных средств, что определяется в результате исследования рынка приборов данного типа, и максимальное улучшение показателя цена/функциональные возможно-

сти. На этом этапе явно или неявно формулируются требования к типу |

|||||

используемого микропроцессора или микроконтроллера. |

|||||

Этап разработки алгоритма является наиболее ответственным, |

|||||

поскольку ошибки этого этапа обнаруживаются при испытании закон- |

|||||

ченного изделия и приводят к дорогостоящей переработке всей МПС. |

|||||

Прорабатывается несколько вариантов алгоритма, обеспечивающих |

|||||

выполнение технических требований с использованием наработанных |

|||||

ранее функционально-топологических модулей. Основные варианты |

|||||

отличаются соотношением объема программного обеспечения и аппа- |

|||||

Технические требования к микропроцессорной системе |

|||||

Коррекция |

|||||

алгоритма |

|||||

управления |

Разработка алгоритма |

Библиотека |

|||

функционально- |

|||||

Разработка структуры аппаратных и |

топологических |

||||

программных средств |

|||||

Коррекция |

Разработка программы |

Разработка аппаратуры |

Коррекция |

||

исходного |

(исходный текст) |

(принципиальныесхемы, |

|||

топология плат) |

|||||

топологии |

|||||

Трансляция программы |

Монтаж макета |

||||

Отладка программы |

Автономная отладка |

||||

на модели |

аппаратуры |

||||

Совместная отладка программных и аппаратных |

|||||

средств системы в реальном масштабе времени |

|||||

Интеграция микропроцессорной системы в изделие |

|||||

Испытание изделия |

|||||

Микропроцессорная система, соответствующая тех- |

|||||

ническим требованиям |

|||||

ратуры. Критерием выбора является реализация максимального числа функций программным способом при наименьших аппаратных затратах, обеспечивающая заданные показатели быстродействия и надежности в полном диапазоне эксплуатационных воздействий. Часто определяющим требованием является возможность размещения кода программы во внутренней памяти микроконтроллера, что позволяет обеспечить его защиту от несанкционированного доступа. На этом этапе окончательно определяется тип микроконтроллера и важнейших схем обрамления (память, ПЛИС, интерфейс, АЦП, и т. п.).

На этапе разработки структуры МПС окончательно определяет-

ся состав имеющихся и подлежащих разработке аппаратных модулей, протоколы обмена между модулями, типы разъемов. Поскольку МПС встраивается в изделие, выполняется предварительная проработка конструкции плат. В части программного обеспечения определяются состав и связи программных модулей, язык программирования. Здесь же производится выбор средств проектирования и отладки.

Стадия создания программы образует внутренний, часто повторяющийся цикл. Она состоит из этапов разработки исходного текста, трансляции, отладки программы на модели и коррекции исходного текста. Содержание этих этапов существенно зависит от используемых системных средств. В настоящее время ресурсы микропроцессоров и микроконтроллеров достаточны для поддержки программирования на языках высокого уровня. Это позволяет использовать все преимущества структурного программирования, разрабатывать программное обеспечение как проект с использованием раздельно транслируемых модулей. В настоящее время самым мощным средством разработки программного обеспечения для микропроцессоров и микроконтроллеров являются интегрированные кросс-системы программирования на языках высокого уровня типа Паскаль, Си. Например, интегрированная система разработки программного обеспечения Паскаль-51 содержит в своем составе редактор текста, компилятор с редактором связей, библиотеку стандартных функций периода выполнения и отладчик. Такие системы позволяют значительно сократить затраты времени на выполнение этого внутреннего цикла. Однако программы, написанные на языках высокого уровня, имеют больший объем и более низкое быстродействие, чем аналогичные программы, написанные на языке ассемблера. Поэтому язык ассемблера продолжает широко использоваться, особенно при ограниченных ресурсах МПС и необходимости обеспечить выполнение контролируемых интервалов времени.

На этих этапах обнаруживаются и устраняются синтаксические и логические ошибки программы. Синтаксические ошибки связаны с нарушением синтаксиса команд, директив транслятора и использованием не определенных ранее меток и имен. Логические ошибки приводят к неправильному функционированию программы. Они связаны с ошибками программы (указан неверный переход при ветвлении, записана не

та команда и т.д.) и ошибками алгоритма. Содержание этих этапов при разработке программ на языке ассемблера приведено ниже.

Стадия создания аппаратуры представляет другой внутренний цикл, выполняемый параллельно с первым. Она содержит разработку общей принципиальной схемы, разводку топологии плат, монтаж макета и его автономную отладку. Эти этапы можно считать завершенными после того, как «оживает» системная магистраль МПС и через нее можно обратиться к памяти, устройствам ввода/вывода. Время выполнения этого этапа зависит от имеющегося набора опробованных функ- ционально-топологических модулей и квалификации разработчика. Распространенными системами проектирования, используемыми на этапе ввода принципиальной схемы и разработки топологии, являются

PCAD и OrCAD (CAD – computer aided design – автоматизированное проектирование). Эффективность работы с ними значительно зависит от имеющегося в распоряжении разработчика объема библиотек используемых элементов.

Этап совместной отладки аппаратуры и программного обеспечения в реальном масштабе времени является самым трудоемким и обязательно требует использования таких высокопроизводительных средств, как внутрисхемный эмулятор, эмулятор ПЗУ, логический анализатор. Выбор одного из перечисленных средств обусловлен используемым методом отладки. На этом этапе выявляются динамические ошибки, возникающие при взаимодействии программных и аппаратных средств в реальном масштабе времени. Эти ошибки обусловлены различными задержками распространения сигналов по линиям системной магистрали и взаимными помехами между линиями, возникающими при их неудачном взаимном расположении. Динамические ошибки обнаружить значительно сложнее из-за нерегулярности их появления.

Для локализации динамических ошибок используются логические анализаторы. Логические уровни сигналов системной магистрали или отдельных шин и линий в режиме приема постоянно записываются в память типа FIFO. Прекращение записи производится при появлении выбранного события (совпадение заданного и фактического адреса на ША, кодов команд на ШД или появление короткого импульса помехи). В это время в памяти содержится вся предшествующая данному событию информация. Анализируя предысторию события, записанную в памяти, можно определить и причину появления сбоя в работе МПС. Информация на дисплее может быть представлена в графическом виде, в виде двоичного, шестнадцатеричного кода или мнемоники команд. Логические анализаторы состояний выполняют запись с тактовой частотой МПС. Для фиксации быстро протекающих процессов используются временные логические анализаторы, у которых тактовая частота записи в память значительно превышает тактовую частоту МПС.

Совместная отладка аппаратных и программных средств в реальном масштабе времени выполняется с помощью эмуляторов ПЗУ и внутрисхемных эмуляторов под управлением инструментальной ЭВМ.

Функции средств отладки

Сроки и качество отладки системы зависят от средств отладки. Чем совершеннее приборы, имеющиеся в распоряжении инженера-разработчика, тем скорее можно начать отладку аппаратуры и программ и тем быстрее обнаружить ошибки, локализовать источники, устранение которых обойдется дороже на более позднем этапе проектирования.

Средства отладки должны:

1) управлять поведением системы или/и ее модели на различных уровнях абстрактного представления;

2) собирать информацию о поведении системы или/и ее модели, обрабатывать и представлять на различных уровнях абстракции;

3) преобразовывать системы, придавать им свойства контролепригодности;

4) моделировать поведение внешней среды проектируемой системы.

Под управлением поведением системы или ее модели понимаются определение и подача входных воздействий для запуска или останова системы или ее модели, для перевода в конкретное состояние последних. Чтобы определить место субъективной неисправности, которая может быть внесена на любой стадии проектирования, необходимо уметь собирать информацию о поведении системы и представлять ее в тех формах, которые приняты для данного проекта. Например, это могут быть вре-менные диаграммы, принципиальные электрические схемы, язык регистровых передач, ассемблер и др.

В общем случае нельзя локализовать источник ошибки проектируемой системы, имея информацию о поведении системы только на ее внешних выводах, поэтому проектируемую систему преобразовывают. Например, прежде чем изготовлять однокристальную микроЭВМ с теми или иными "зашивками" ПЗУ, программы отлаживают на эмуляционном кристалле, у которого магистраль выведена на внешние контакты и вместо ПЗУ установлено ОЗУ.

Микропроцессорные системы по своей сложности, требованиям и функциям могут значительно отличаться надежностными параметрами, объемом программных средств, быть однопроцессорными и многопроцессорными, построенными на одном типе микропроцессорного набора или нескольких, и т.д. В связи с этим процесс проектирования может видоизменяться в зависимости от требований, предъявляемых к системам. Например, процесс проектирования МПС, отличающихся одна от другой содержанием ПЗУ, будет состоять из разработки программ и изготовления ПЗУ.

При проектировании многопроцессорных микропроцессорных систем, содержащих несколько типов микропроцессорных наборов, необходимо решать вопросы организации памяти, взаимодействия с процессорами, организации обмена между устройствами системы и внешней средой, согласования функционирования устройств, имеющих различную скорость работы, и т. д. Ниже приведена примерная последовательность этапов, типичных для создания микропроцессорной системы:

1. Формализация требований к системе.

2. Разработка структуры и архитектуры системы.

3. Разработка и изготовление аппаратных средств и программного обеспечения системы.

4. Комплексная отладка и приемосдаточные испытания.

Этап 1. На этом этапе составляются внешние спецификации, перечисляются функции системы, формализуется техническое задание (ТЗ) на систему, формально излагаются замыслы разработчика в официальной документации.

Этап 2. На данном этапе определяются функции отдельных устройств и программных средств, выбираются микропроцессорные наборы, на базе которых будет реализована система, определяются взаимодействие между аппаратными и программными средствами, временные характеристики отдельных устройств и программ.

Этап 3. После определения функций, реализуемых аппаратурой, и функций, реализуемых программами, схемотехники и программисты одновременно приступают к разработке и изготовлению соответственно опытного образца и программных средств. Разработка и изготовление аппаратуры состоят из разработки структурных и принципиальных схем, изготовления прототипа, автономной отладки.

Разработка программ состоит из разработки алгоритмов; написания текста исходных программ; трансляции исходных программ в объектные программы; автономной отладки.

Этап 4. см. Комплексная отладка.

На каждом этапе проектирования МПС людьми могут быть внесены неисправности и приняты неверные проектные решения. Кроме того, в аппаратуре могут возникнуть дефекты.

Процессы автоматизации технического оборудования захватили большую часть всей организации производства. Они применяются повсеместно в станках, машинах и механизмах, робототехнических комплексах. Новые технологии существенно повышают производительность труда, уменьшая влияние человеческого фактора на риски при производстве. Также повышается технический уровень и качество продукции. Микропроцессорные системы – в своё время была инновационной технологией. Но сейчас это уже обыденность, ведь приборы, которые выполнены с применением микропроцессоров, имеют более высокие показатели в работе по сравнению с приборами, выполненными на отдельных логических схемах, при экономической выгоде первых.

Стандартизация процесса разработки упрощает анализ и исследования в этой сфере. А также делает наглядным текущее состояние и возможный результат. Современные компании, занимающиеся разработкой встраиваемых микропроцессорных систем используют программируемые логические интегральные схемы (ПЛИС) и системы автоматизированного производства для быстрого и организованного проектирования. При помощи ПЛИС возможна также отладка и тестирование в режиме реального времени. Ежегодное обновление САПР позволяет всё меньше и меньше тратить время на монотонную и односложную работу, при этом, не допуская очевидные ошибки. Это позволяет абстрагироваться на более высокие уровни системы и решение тяжелых задач.

Процесс разработки встраиваемых микропроцессорных систем можно представить в виде двух маршрутов последовательных этапов проектирования. Первый маршрут - разработка аппаратной части встраиваемой микропроцессорной системы. Второй маршрут - проектирование программных средств (рис.1).

Рисунок 1. Этапы проектирования

Но не все ступени маршрута обязательны. Моделирование аппаратной части системы в процессе разработки может не проводиться. Поэтому можно исключить некоторые ступени: подготовка спецификации моделирования, генерация моделей, функционального и временного моделирование. При этом следует учитывать, что моделирование аппаратной части системы повышает эффективность процесса проектирования в целом за счет более раннего обнаружения возможных ошибок и их устранение.

Типичные этапы проектирования микропроцессорных систем включают:

- Формализация различных требований к системе. Необходимо составить внешние спецификаций, техническое задание (ТЗ) на систему, заметки образа системы разработчиком в документации, перечисляются функции системы.

- Разработка структуры и архитектуры элементов системы. Необходимо определить взаимодействие между аппаратными и программными средствами, функции периферии и программных оболочек, выбрать микропроцессорные решения, на базе которых будет реализована система, определить временные характеристики.

- Разработка и изготовление аппаратной части и программного обеспечения системы. Необходимо разработать структуру и принципиальные схемы, изготовить прототип, отладить в условиях базовых режимов работы. Разработка программного обеспечения должна состоять из алгоритмов, написания текста исходных программ, трансляции исходных программ в объектные программы, программной отладки и симуляции.

- Общая отладка и приемосдаточные испытания в рабочих условиях.

Человеческий фактор допускает неисправности и принятие неверных проектных решений. Также существуют аппаратурные дефекты в устройствах. Например, возможны следующие источники ошибок на этапах:

Этап 1. Логическая несогласованность требований, упущения, неточности алгоритма.

Этап 2. Упущения функций, упущение некоторых информационных потоков, несогласованность протокола взаимодействия аппаратуры и программ, неверное определение технических требований, неверный выбор микропроцессорных решений, неточности алгоритмов.

Этап 3. При разработке аппаратуры - упущение некоторых функций, неверная интерпретация технического задания, недоработки в схемах синхронизации, нарушение правил проектирования; при разработке программных средств - упущения некоторых функций технического задания, неточности в алгоритмах, неточности кодирования; при изготовлении прототипа - неисправности комплектующих изделий и периферии, неисправности монтажа и сборки.

Каждый из перечисленных источников ошибки может повлечь за собой большое число физических или субъективных неисправностей, которые необходимо в дальнейшем определить и устранить. Обнаружение и локализация неисправности осложняется по нескольким причинам: во-первых, из-за неисправностей может быть несколько; во-вторых, однообразие симптомов различных проблем. Так как отсутствуют модели субъективных неисправностей, указанная задача не формализована. Возможно решение при помощи экспертных систем – базы данных с уже имеющимися проблемами и их решением, исходящим из практического опыта.

Субъективные неисправности отличаются от физических тем, что после обнаружения, локализации и коррекции больше не возникают. Но субъективные неисправности могут быть внесены на этапе разработки спецификации системы, а это означает, что даже после самых тщательных испытаний системы на соответствие ее спецификациям в системе могут находиться субъективные неисправности.

Процесс проектирования - итерационный процесс, а значит при неполном устранении ошибок на одном этапе, возможно их появление на следующем. Обнаруживать неисправности необходимо как можно раньше, для этого надо контролировать корректность проекта на каждом этапе разработки. Например, неисправности, обнаруженные на конечном этапе приема-сдачи проекта, могут привести к коррекции спецификаций, а, следовательно, к началу проектирования всей системы. К таким же последствия приводят изменения технического задания (из-за недосказанности и недостатка сведений о системе).

Основными методами контроля правильности проектирования являются: верификация, моделирование и тестирование.

Верификация позволяет обнаруживать не только текущие ошибки, но и потенциальные ошибки, которые могут появиться в будущих проектах с использованием блоков. Но требует отдельного технического задания и соответствующие навыки и подходит под крупные проекты. На небольших проектах чаще используют моделирование поведения объекта и тестирование, т.к. этот вариант экономически выгоден и не требует большого количества ресурсов.

Контроль корректности достигается на каждом этапе проектирования необходимостью проведения моделирования на различных уровнях абстракций системы и проверки правильности реализованной части модели путем тестирования. Функциональная спецификация может моделироваться и проверяться в опытном порядке для выявления ожидаемого результата. Также может проводиться анализ коллективом экспертов. После утверждения функциональной спецификации начинается разработка функциональных тестов системы, предназначенных для установления правильности функционирования системы в соответствии с ее функциональной спецификацией. Наиболее эффективно разрабатывать тесты, целиком основанные на этой спецификации, поскольку это даёт возможность проверки любой реализации системы, способной выполнять функции, оговоренные в спецификации. Этот способ - аналогичен другим, где тесты строятся применительно к конкретным реализациям, но точнее проводит сопоставление ожидания и результата разработки.

После обнаружения ошибки должен быть локализован ее источник для проведения коррекции на соответствующем уровне абстрактного представления системы и в соответствующем месте. Неправильное определение источника ошибки или проведение корректировок на другом уровне абстрактного представления системы приводит к тому, что информация о системе на верхнем уровне становится ошибочной и не может быть использована для дальнейшей отладки при производстве и эксплуатации системы.

Автоматизация монотонной работы по разработке тестовых программ сокращает период конструирования и отладки за счет более раннего получения тестов (поскольку они могут быть сгенерированы сразу после формирования требований к системе) и позволяет проектировщику изменять спецификации без переписывания всех тестовых программ. На практике разработка тестов менее приоритетна по сравнению с проектом, поэтому тестовые программы появляются значительно позже его завершения.

Таким образом, учитывая нюансы проектирования микропроцессоров можно легко обойти «подводные камни» при разработке. Использование программируемых логических интегральных схем (ПЛИС) облегчает отладку еще не выпущенной партии и позволяет протестировать проект и исправить недочеты. А системы автоматизированного производства (САПР) упрощает разработку, позволяя перераспределить ресурсы более рационально.

Список литературы:

- СибГУТИ [Электронный ресурс] / Проектирование микропроцессора на ПЛИС – Режим доступа: http://ict.sibsutis.ru/sites/csc.sibsutis.ru/files/courses/mps/mp.pdf–свободный. – загл. с экрана. – яз. рус. (дата обращения 22.12.2017).

- Зотов В. Embedded Development Kit - система проектирования встраиваемых микропроцессорных систем на основе ПЛИС серий FPGA фирмы Xilinx. 2004. № 3.